计算机与信息安全导论第四章-门和电路

1. 计算机和电路

门:对电信号基本运算的设备

电路:由门组合而成

描述门和电路的三种表示法:布尔代数,逻辑框图,真值表

2.门

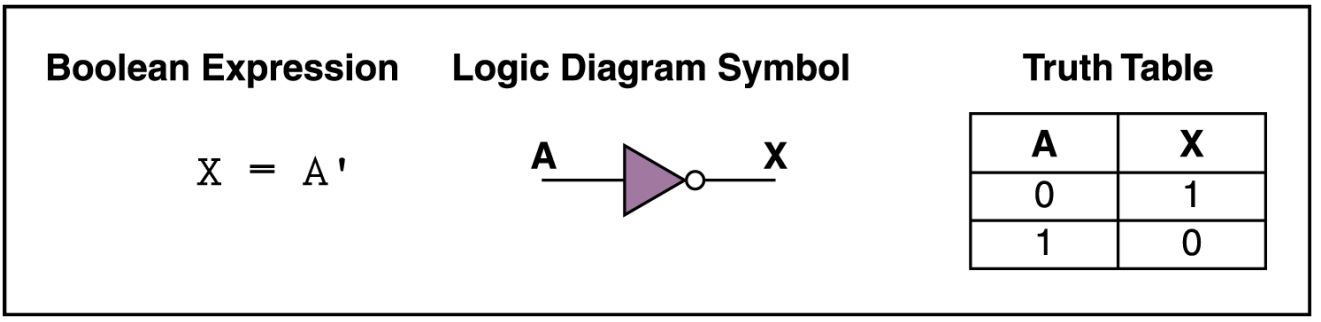

2.1 非门

非门接收一位(0或1)并返回相反的值

2.2 与门

与门接收两位输入,如果全为1,输出1;否则输出0

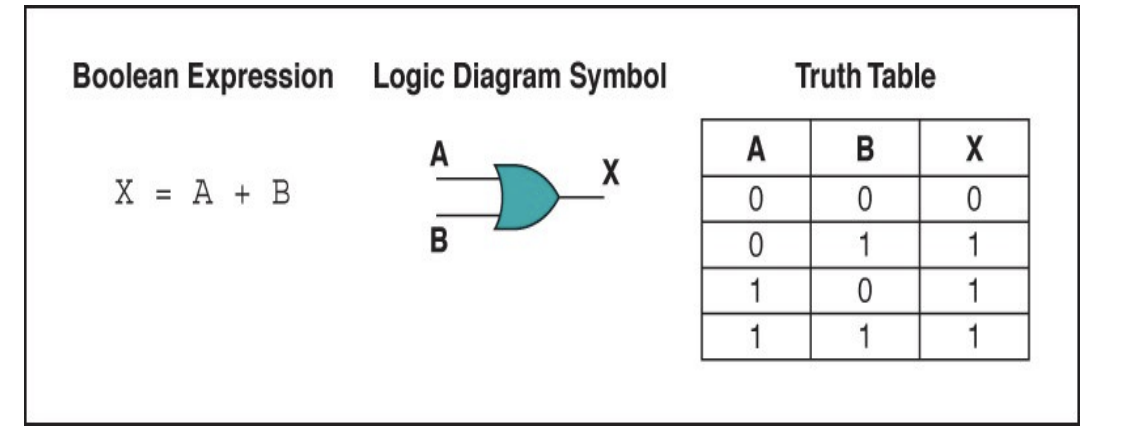

2.3 或门

接收两位输入。如果全为0,输出为0;否则输出位为1

2.4 异或门

异或门接收两位输入

如果两位相同,则输出为0,;否则输出为1

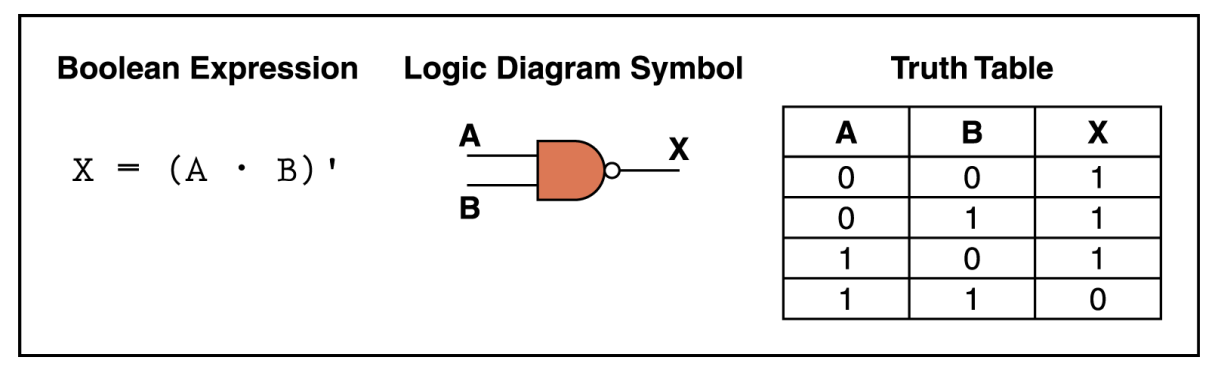

2.5 与非门

与非门接收两位输入

如果全为1,输出为0;否则,输出为1

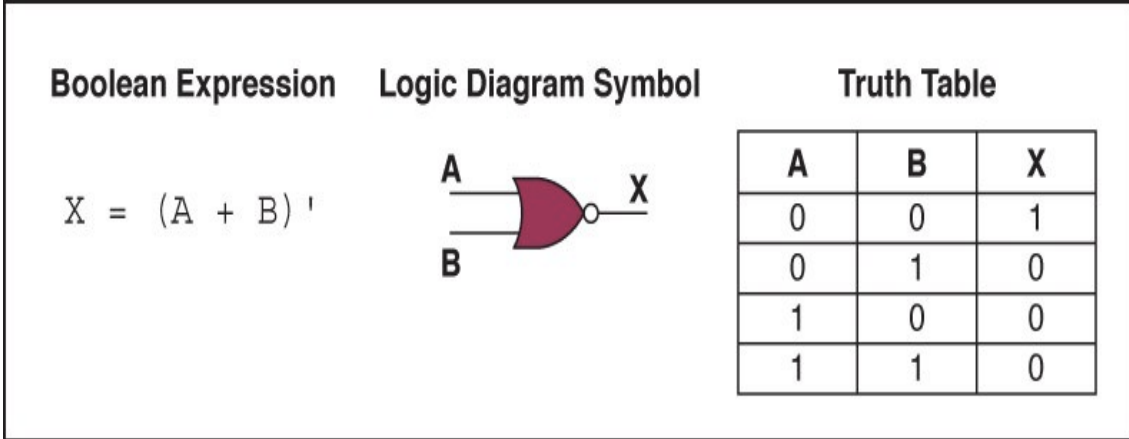

2.6 或非门

或非门接收两位输入

如果全为0,输出为1;否则,输出为0

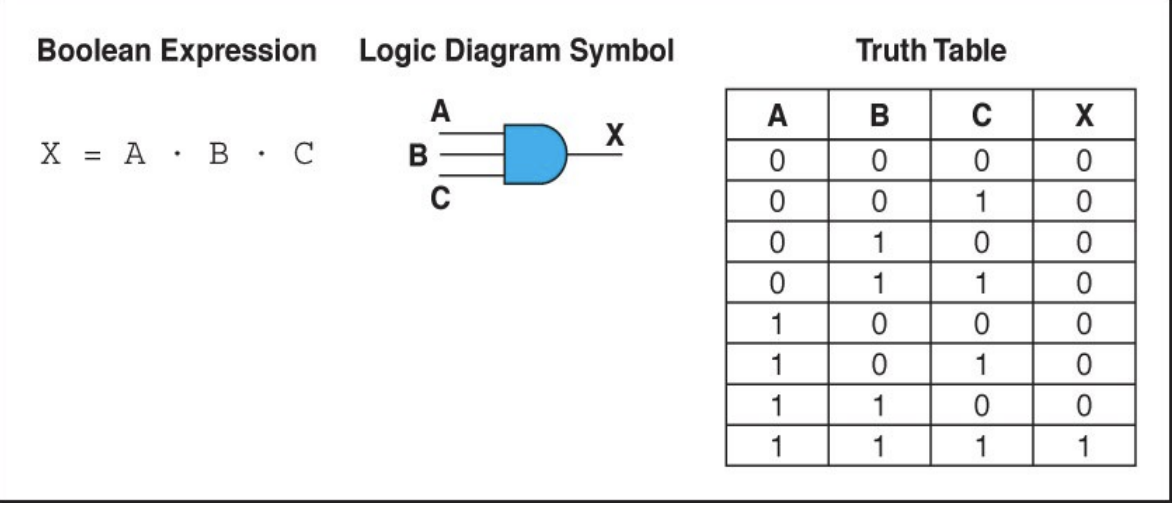

2.7 有三个输入的门

2.8 总结

非门(NOT Gate):对输入值取反。

与门(AND Gate):当且仅当两个输入值均为1时,输出1;否则输出0。

或门(OR Gate):当任意输入为1时,输出1;否则输出0。

异或门(XOR Gate):当两个输入值不同时输出1;相同时输出0。

与非门(NAND Gate):与门的反向,两个输入值都为1时输出0,否则输出1。

或非门(NOR Gate):或门的反向,两个输入值都为0时输出1,否则输出0。

3.门的构造

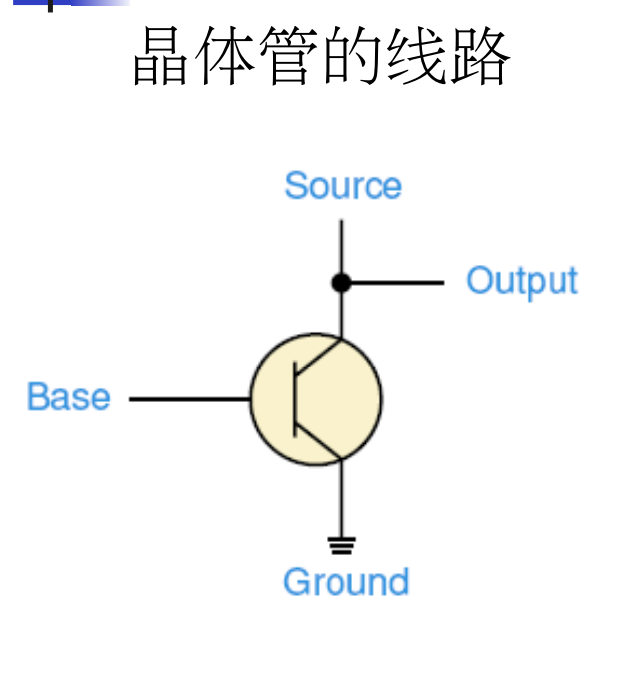

晶体管:作为导线或电阻器的设备,有输入信号的电压电平决定它的作用

半导体:既不是良好的导体也不是绝缘体的材料,如硅

3.1 晶体管的线路

晶体管有三个终端:源极、基极、发射极

基极信号为高电压时,输出值为0。

基极信号为低电压时,输出值为1。

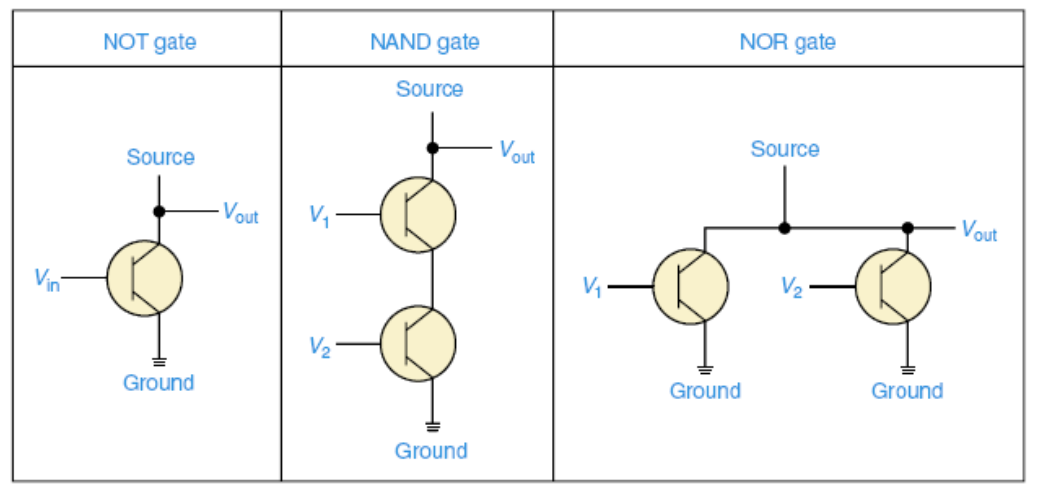

3.2 使用晶体管构造门

4.电路

4.1 组合电路

输出仅由输入值决定的电路

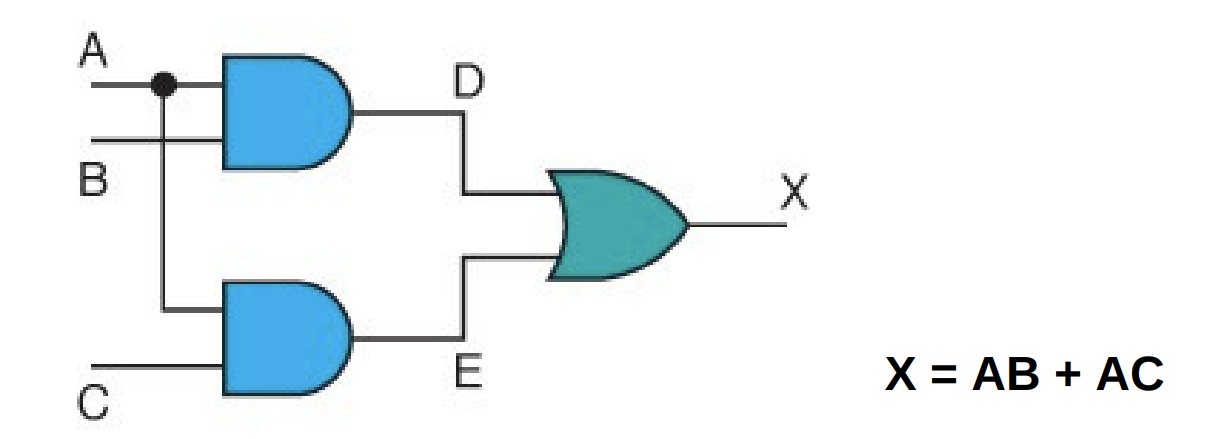

通过将一个门的输出值作为另一个门的输入值形成电路:

时序电路指输出是输入值的和电路当前状态的函数的电路

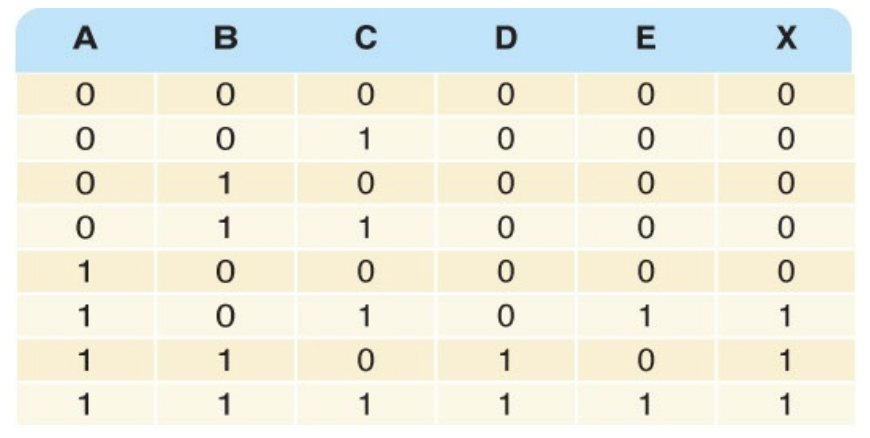

三个输入需要八行来描述所有可能的输入组合

- 等价电路:对于每个输入值组合,两个电路都生成完全相同的输出;这种现象证明了布尔代数的一个重要属性——分配率A(B + C) = AB + AC

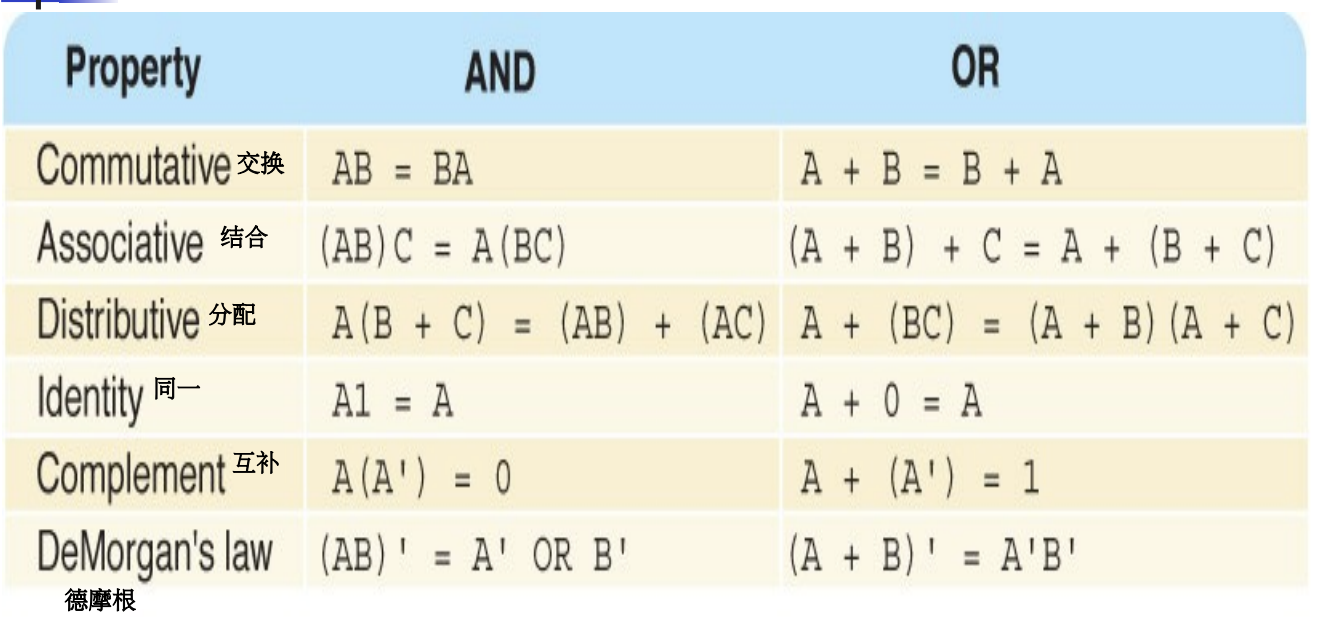

4.2 布尔运算的性质

4.3 各类电路

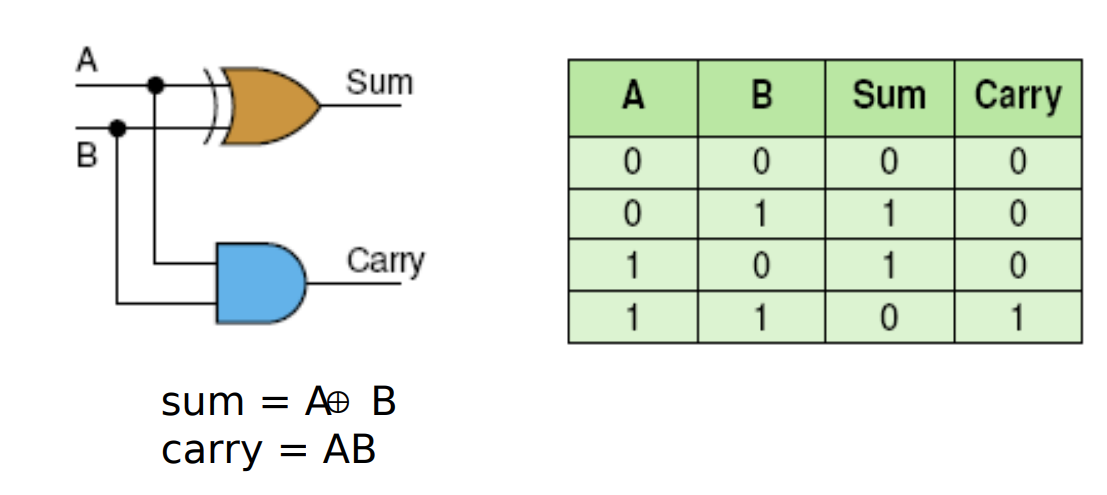

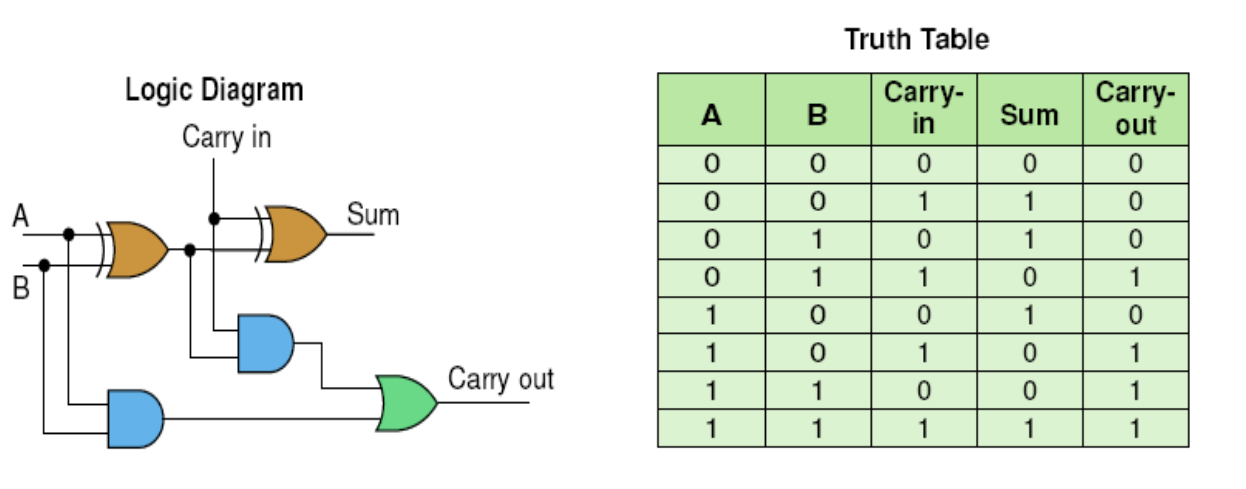

加法器:对二进制执行加法运算的电路

半加器:计算两个数位的和,并生成正确进位的电路

全加器:计算两个数位的和,并考虑进位输入的电路

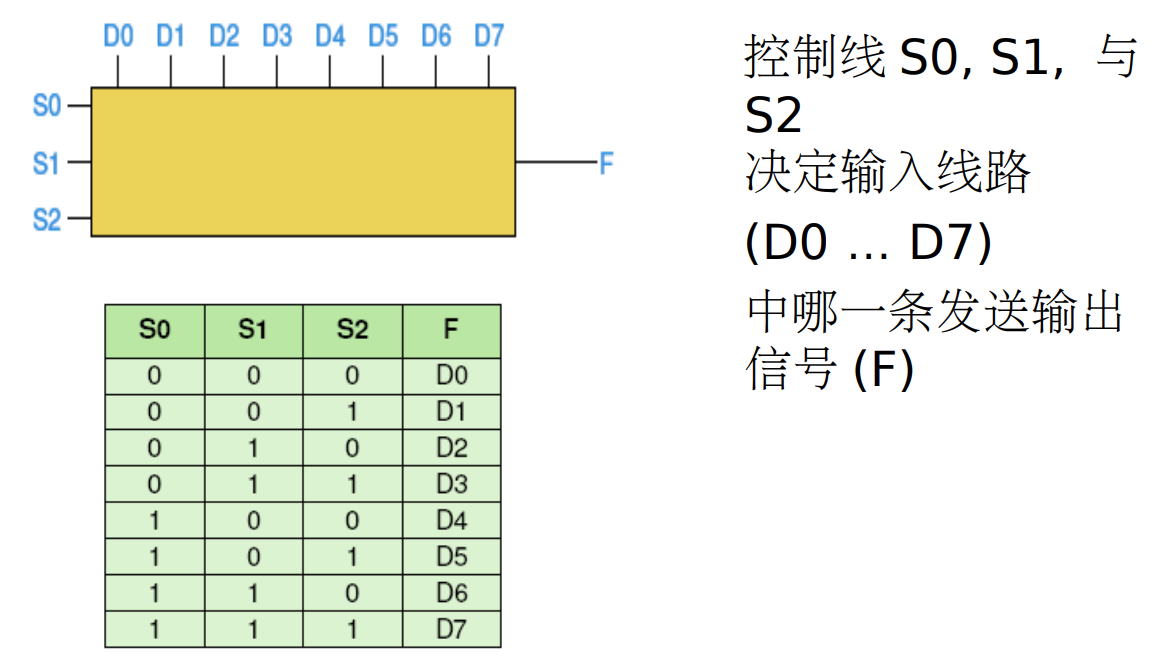

多路复用器:使用一些输入控制信号决定用哪条输入数据线发送输出信号的电路

5.存储器电路

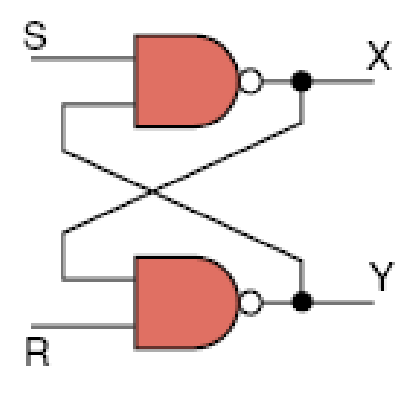

S-R锁存器:一种用于存储一个比特(bit)(二进制数字)的电路。S-R锁存器有两个输出,它们总是互补的。

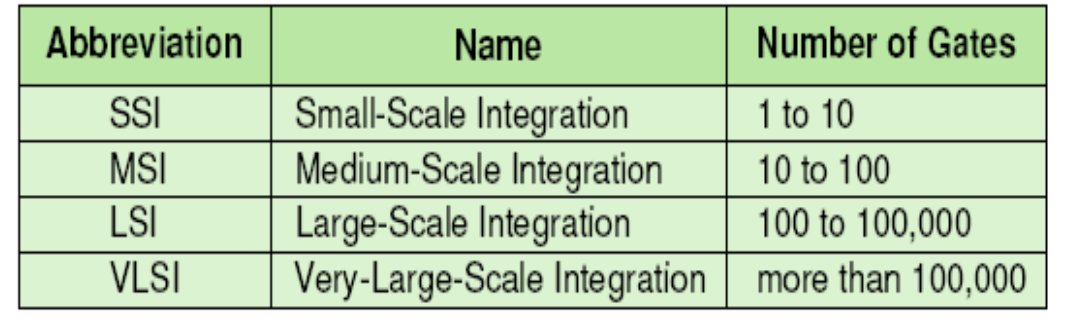

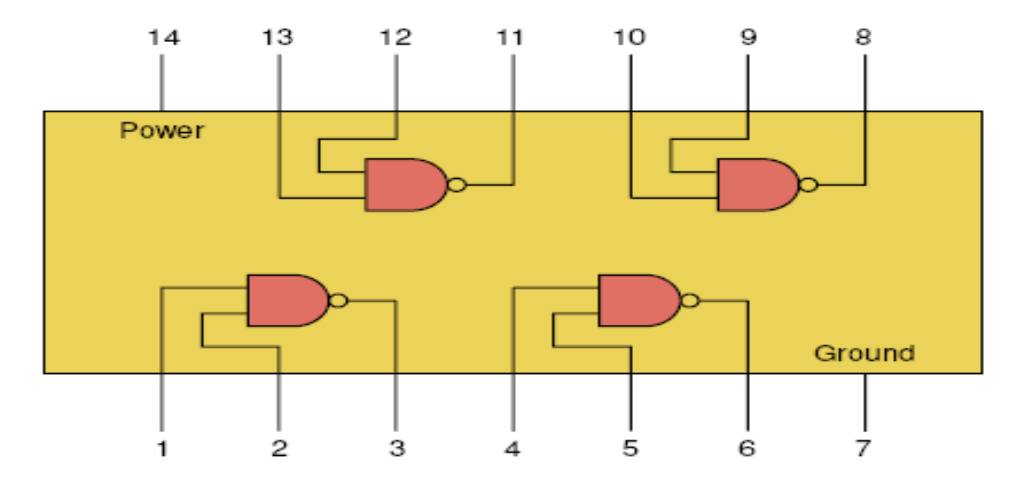

6. 集成电路

集成电路,又称芯片,是嵌入了多个门的硅片。

小规模集成芯片

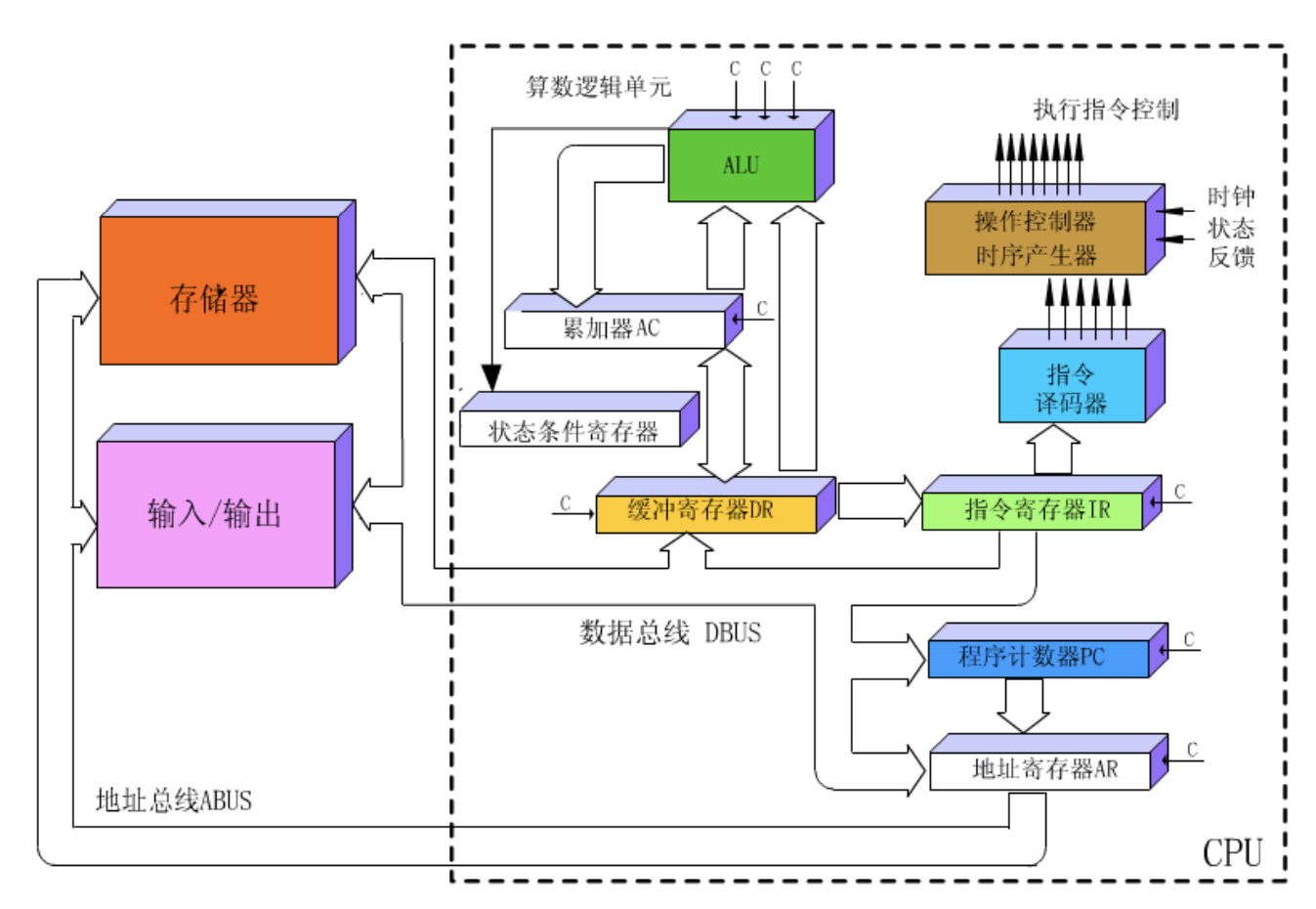

7.CPU芯片

- CPU是一种具有输入线和输出线的高级电路

- 每一个CPU芯片有大量的引脚,计算机系统的所有通信都是通过这些引脚完成的

7.1 CPU功能

功能1-指令控制:程序的顺序控制称为指令控制。由于程序是一个指令序列,这些指令的相互顺序不能任意颠倒,必须严格按程序规定的顺序进行。

功能2-操作控制:一条指令由若干操作信号的组合实现,CPU产生并管理这些信号,把各种操作信号送往相应的部件,从而控制这些部件按指令的要求进行动作。

功能3-时间控制:对各种操作实施时间上的定时称为时间控制。在计算机中,各种指令的操作信号以及一条指令的整个执行过程都受到时间的严格定时。此外,指令的执行过程需要时间控制。

功能4-数据加工:对数据进行算术运算和逻辑运算处理

7.2 CPU组成

控制器:由程序计数器、指令寄存器、指令译码器、时序产生器和操作控制器组成,它是发布命令的“决策机构”

,即完成协调和指挥整个计算机系统的操作。它的主要功能有:

- 从内存中取出一条指令,并指出下一条指令在内存中的位置:

- 对指令进行译码或测试,并产生相应的操作控制信号,以便启动规定的动作

- 指挥并控制 CPU、内存和输入/输出设备之间数据流动的方向。

运算器:由算术逻辑单元(ALU)、累加寄存器、数据缓冲寄存器和状态条件寄存器组成。它是数据加工处理部件

相对控制器而言,运算器接受控制器的命令而进行动作,即运算器所进行的全部操作都是由控制器发出的控制信号来指挥的,所以它是执行部件。运算器有两个主要功能:

- 执行所有的算术运算

- 执行所有的逻辑运算,并进行逻辑测试。

7.3 CPU中的主要寄存器

- 数据缓冲寄存器(DR )

- 指令寄存器(IR)

- 程序计数器(PC)

- 地址寄存器(AR)

- 状态条件寄存器(PSW)

7.4 操作控制器与时序产生器

7.5 CPU主要的性能指标

- 主频:主频也叫时钟频率,单位是MHz,GHz,用来表示CPU的运算速度。

CPU的主频 = 外频 x倍频系数 - 外频:外频是CPU的基准频率。CPU的外频决定着整块主板的运行速度

- 前端总线频率

- 倍频系数

- 缓存